掌握VHDL語(yu)言 北京(jing)理(li)工大學(xue)《集(ji)成電(dian)路(lu)設計實踐壹》軟(ruan)件(jian)開(kai)發的核心(xin)

- 設計輸入:學(xue)生(sheng)使用集(ji)成開(kai)發(fa)環(huan)境(jing)(如(ru)Intel Quartus Prime、Xilinx ISE/Vivado),將電(dian)路(lu)構思(si)轉(zhuan)化(hua)為結構清(qing)晰、符(fu)合(he)規範(fan)的(de)VHDL代碼(ma)。這要(yao)求熟(shu)練(lian)掌握VHDL的基本(ben)結構(實體、結構體(ti))、數據(ju)類型、並(bing)行(xing)語(yu)句和順(shun)序(xu)語(yu)句。

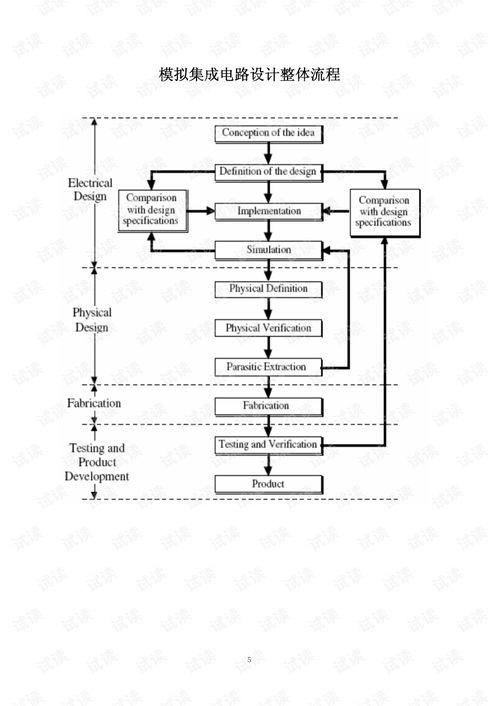

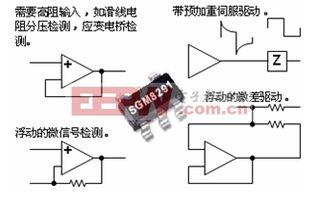

- 功(gong)能(neng)仿(fang)真:編寫測試(shi)平(ping)臺(tai)(Testbench),對設計模塊施(shi)加(jia)激(ji)勵(li)信號(hao),通(tong)過(guo)軟(ruan)件(jian)仿(fang)真驗證其(qi)邏輯功(gong)能(neng)的正(zheng)確性。這個階(jie)段(duan)完(wan)全(quan)在軟(ruan)件(jian)環(huan)境(jing)中進(jin)行,是(shi)排查(zha)邏輯錯誤的(de)關(guan)鍵,深刻體現(xian)了“軟(ruan)件(jian)開(kai)發”中的(de)調試(shi)與驗證思(si)想(xiang)。

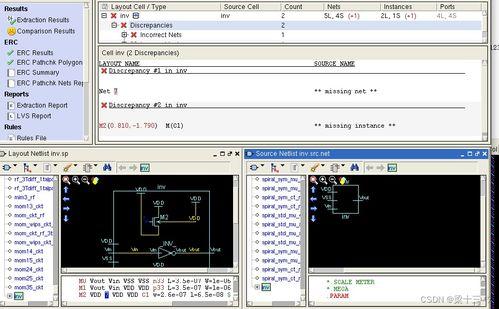

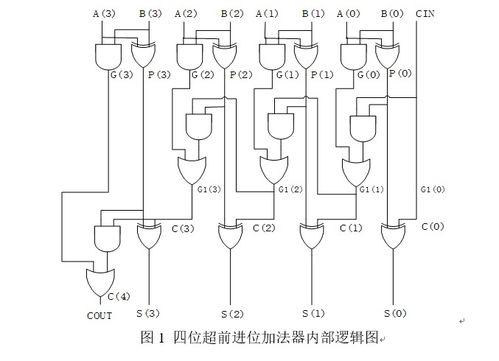

- 綜合(he)與實現:利用綜(zong)合(he)工具(ju),將行為級的VHDL描述(shu)“編譯(yi)”和優(you)化(hua)成(cheng)目(mu)標工藝(yi)(如FPGA)對應的(de)門級網(wang)表。這個過(guo)程(cheng)將抽象(xiang)的(de)代碼(ma)映(ying)射為具(ju)體(ti)的(de)硬(ying)件(jian)資源,是(shi)硬(ying)件(jian)設計軟(ruan)件(jian)化(hua)的(de)核心(xin)體現(xian)。

- 時序分(fen)析與下(xia)載測試(shi):對綜合(he)後(hou)的(de)設計進(jin)行時序分(fen)析,確保(bao)滿足(zu)時鐘頻(pin)率(lv)要(yao)求,最終(zhong)將生(sheng)成的(de)配置(zhi)文(wen)件(jian)下(xia)載到FPGA開發(fa)板(ban)進行實物驗證。

- 理(li)解硬(ying)件(jian)思(si)維(wei):牢(lao)記VHDL描述(shu)的是(shi)並行(xing)執(zhi)行的(de)硬(ying)件(jian)電(dian)路(lu),這與傳(chuan)統(tong)串行(xing)執(zhi)行(xing)的軟(ruan)件(jian)編(bian)程有(you)本(ben)質區(qu)別。清(qing)晰的(de)硬(ying)件(jian)結構觀(guan)念(nian)是(shi)寫出高(gao)效、可(ke)綜(zong)合(he)代碼(ma)的基礎(chu)。

- 熟(shu)練(lian)核心(xin)語(yu)法(fa)與(yu)設計模式:深入(ru)理(li)解進(jin)程(cheng)、信號(hao)與變量(liang)的區(qu)別,掌握有(you)限(xian)狀態機(ji)、數據(ju)路(lu)徑(jing)等(deng)經(jing)典結構的(de)VHDL實現方(fang)法(fa)。

- 善(shan)用開(kai)發(fa)工具(ju):熟(shu)悉(xi)IDE的工(gong)程管理(li)、仿(fang)真調試(shi)、綜合(he)約束(shu)等(deng)各項功(gong)能(neng),能高(gao)效利用工(gong)具(ju)定位和解決(jue)問(wen)題。

- 實踐驅動(dong)學(xue)習:通(tong)過(guo)完(wan)成(cheng)課程中從(cong)簡單組合(he)電(dian)路(lu)到復(fu)雜數字系(xi)統(tong)(如(ru)小(xiao)型CPU、通(tong)信接口(kou))的壹(yi)系列(lie)設計項(xiang)目(mu),在實踐中鞏(gong)固和深化(hua)對VHDL語(yu)言的理(li)解與(yu)應(ying)用能(neng)力(li)。